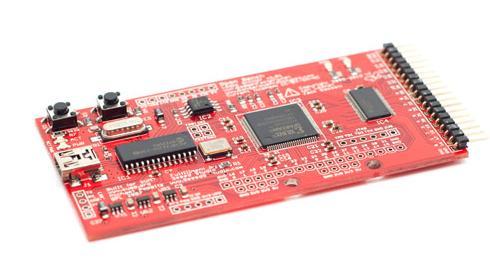

OpenBench Logic Sniffer v1.01

Ottimo complemento del BusPirate è l'analizzatore di stati logici.

Ottimo complemento del BusPirate è l'analizzatore di stati logici.

Che ne dite di un analizzatore a 32 canali @ 100Msps (o 16 @ 200Msps) per 50$? Un sogno? No, un'altra creazione DangerousPrototypes realizzata da SeeedStudio!

Il software in dotazione (scritto in Java per supportare sia Win che Linux e Mac) comprende già vari analizzatori di protocollo:

- 1-wire

- I2C

- SPI

- UART

È comunque piuttosto semplice crearne altri.

Non è invece banale la procedura di aggiornamento per Linux: le istruzioni non sono troppo chiare e ci ho messo un bel pezzo per capire che per l'aggiornamento del codice nel PIC bisognava cortocircuitare le piazzole PGC e PGD invece di premere il tasto "update" (come invece è da fare per l'aggiornamento del codice nell'FPGA). Se a questo si aggiunge che la procedura descritta sul sito richiede un certo sforzo "programmatorio" (la patch fornita genera un reject), si vede che non è proprio da tutti. In compenso, la procedura per Win non sono proprio riuscito ad utilizzarla

Un problema diverso è legato all'uso di OLS, "evoluzione" della GUI originale. Pur avendo dato i permessi giusti a /dev/ttyACM0 (ho anche provato creando /dev/OLS "copiando" i dati di /dev/ttyACM0 ed assegnandogli staticamente il mio utente come proprietario!) continuavo a ricevere un errore:

[28/01/11 15.13.13 - WARN - LogicSnifferDeviceController]: Capture aborted: Failed to open/use /dev/ttyACM0! Possible reason: Unknown Linux Application.

Dopo parecchio scancheramento, ho trovato la soluzione (che ovviamente è semplicissima): basta aggiungere l'utente al gruppo a cui appartiene anche /var/lock e tutto inizia a funzionare a dovere! La spiegazione è nascosta nel funzionamento di una libreria: in pratica il messaggio vorrebbe significare che la porta è lockata da un'applicazione sconosciuta... Sarebbe stato molto più semplice e chiaro un messaggio tipo "Can't create lockfile in /var/lock"...

La versione "base" monta solo un buffer per 16 canali. Per poter usare gli altri 16 o ci si "accontenta" di monitorare solo segnali a 3.3V o si aggiunge un'ala con un ulteriore buffer che tollera i 5V.

A bordo dell'FPGA sono disponibili 276KB di RAM per memorizzare i campioni. Purtroppo, per ragioni di compatibilità con SUMP (che supporta solo buffer con dimensioni pari a potenze di 2) è possibile avere solo buffer di 16K (8ch), 8K (16ch) o 4K (32ch) invece del massimo di 24/12/6K. Comunque il firmware è in evoluzione ed al momento stanno lavorando anche sulla compressione RLE dei sample, che permetterà di acquisire ad alta risoluzione segnali lenti correlandoli con precisione.

Una funzione che può essere molto utile è la possibilità di creare trigger complessi, anch'essa in evoluzione.

Insomma, un prodotto che sicuramente vale più di quel che costa, dato che arriva a competere con prodotti che costano dieci volte tanto.

A volergli trovare dei difetti si può dire che ha poca memoria e non ha un contenitore (anche perché potendo montare o meno il secondo buffer, fargli un contenitore generico non è facile).

Un'ulteriore (ventilata) estensione che potrebbe risultare interessante è un modulo oscilloscopio da mettere al posto del secondo buffer, ma temo che per questo ci vorrà ancora parecchio. Anche se un paio di canali ad 8 bit, da usare a 100Msps... SLURP!